Accelerating the Accelerator:

Automated Static Checking for Regular-Structure Synchronous Accelerator

SSO Symposium Case Study by Igor Arsovski of Groq

Case Study Overview

Igor Arsovski of Groq presented at Real Intent’s 2023 Static Sign-Off Symposium on how Groq uses automated static checking for their regular-structure synchronous accelerator.

Below are text and graphic highlights of what he presented. Real Intent Ascent Lint, Meridian CDC and Meridian RDC were deployed.

The video has the following chapters:

- AI compute needs & Groq’s AI chip

- Groq’s Lint, CDC & RDC sign-off flow

- Results from Groq’s static sign-off flow

- Future static sign-off needs

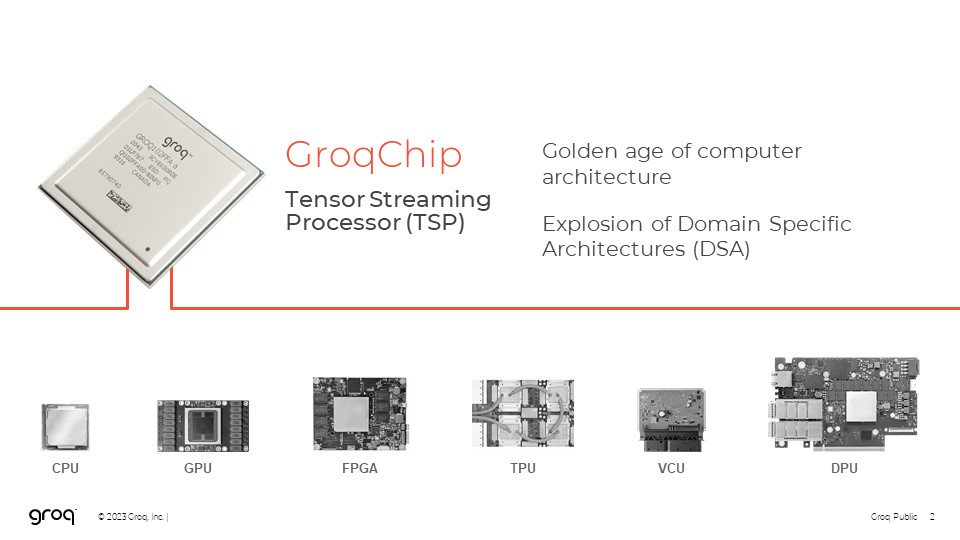

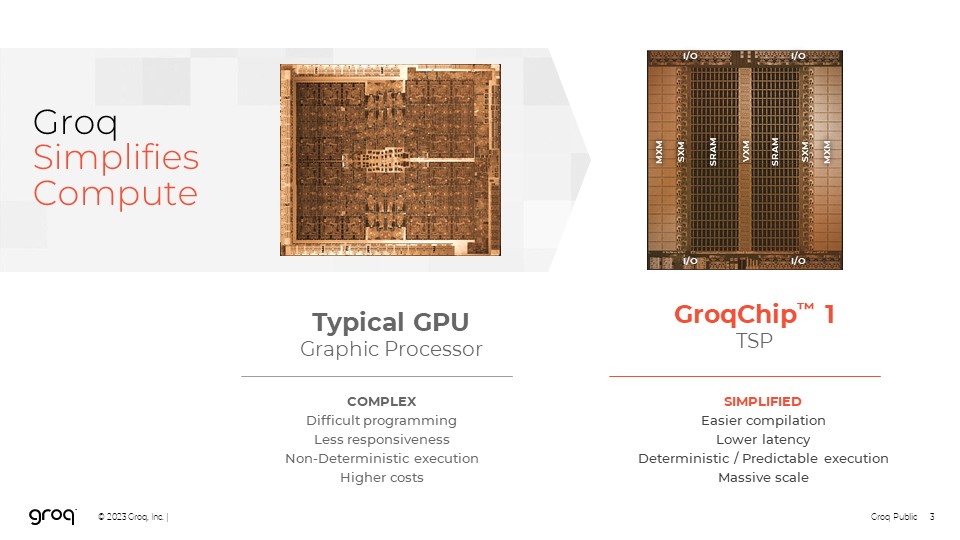

Groq’s Simplified Chip Architecture

Groq’s chip has a very simplified, domain-specific architecture

- Slide 1: AI compute demand

- Slide 2: Domain-specific architectures

- Slide 3: Groq’s simplified architecture

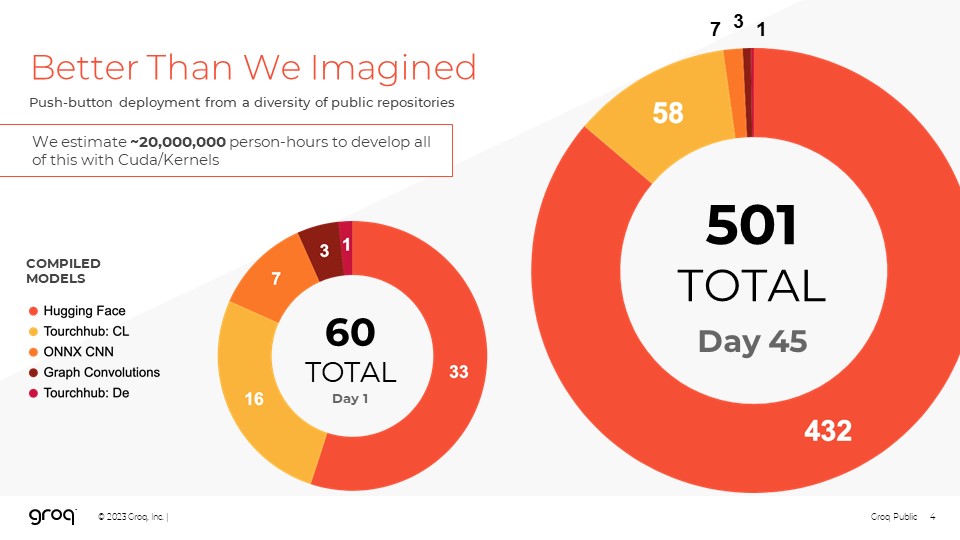

- Slide 4: Rapid AI model compilation

[Toggle the slides to view Groq’s technology background graphics and explanations.]

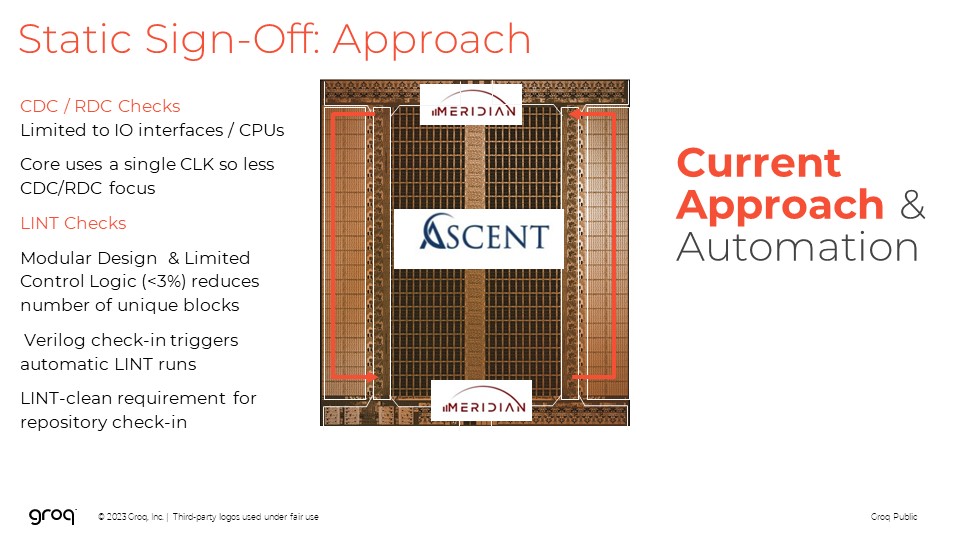

Groq’s Static Sign-off Methodology

Our chip’s regular nature enables us to focus even our static sign off and simplify that as well.

The top and the bottom of the chip is where you see most of the asynchronous interfaces. This is where we focus our clock domain crossing sign-off with Meridian CDC and our reset domain crossing sign-off with Meridian RDC.

And then the rest of the core is running on a single clock, so there are no different clock domain crossings. So here we can focus on RTL linting to get the maximum benefit out of that.

We have repeated blocks, which streamline how quickly we can move through static sign-off. We engage with [Real Intent Ascent Lint] very early in the flow.

This is all automated, so we maintain our repositories to always be lint clean. As soon as someone makes a change in RTL, we automatically launch RTL linting and other checks to make sure the RTL is clean before it is checked in into our golden repository.

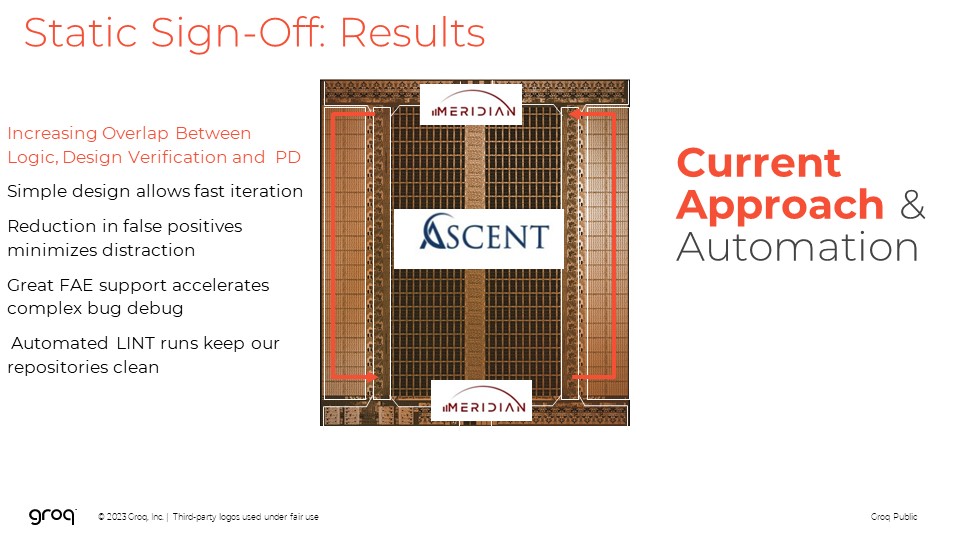

Results — Groq static sign off methodology

Using this approach, we’ve been able to really increase the speed of our iterations. We have really enjoyed the [Real Intent] tools from the aspect of reduction in false positives. This minimizes distractions for our logic team.

We also have really good FAE support. Let’s face it every EDA tool is going to have their bugs — it’s how fast the response is to address these bugs that makes the difference of how we pick our vendors.

As I mentioned, the automated lint really keeps our repositories always clean and ready to kind of tape out. So, we’re always kind of keeping the cleanest possible state of our blocks. So that’s our current static sign-off approach.

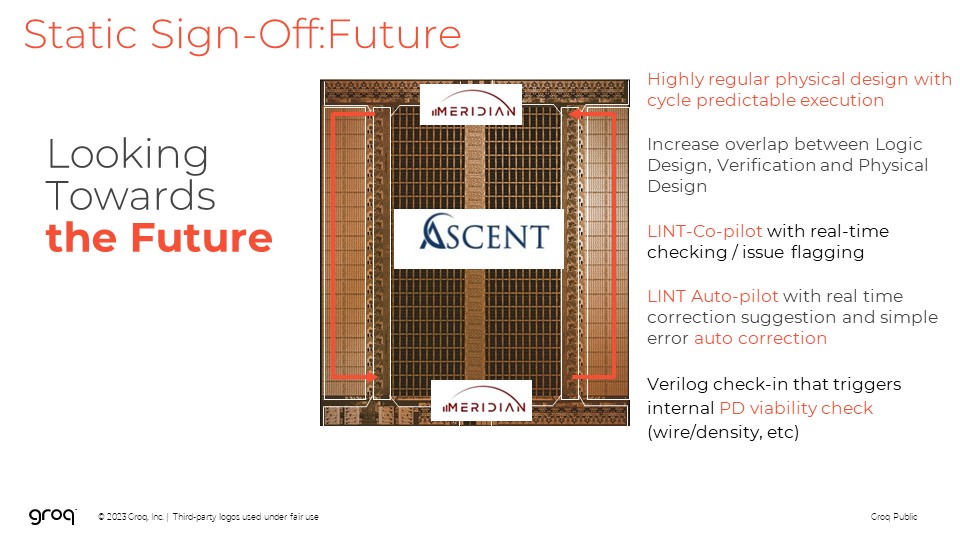

Conclusion – Future Static Sign-Off Vision

What we want to see in the future is an increase in the overlap between logic design verification and physical design. We would love to see lint co-pilots or autopilots that are constantly managing as we write RTL code, so we get that feedback immediately.

We would love to see suggestions of how we would fix some of these problems that are identified by lint. We’d love to get even further shift left right so basically get the feedback on the fly.

I would love the ability to stack logic design verification and physical design and compress those time-to-market cycles. For example, potentially do some light synthesis, and provide feedback on how wire-constrained we are like, what are the flop-to-flop logic stages? Can we actually get feedback on power, maybe suggest assertions that need to be coded into specific blocks, and even implement those?

These are ideas where you can argue you can use AI to help the next generation of AI accelerators.