Multimode Clock Domain Crossing Sign-off

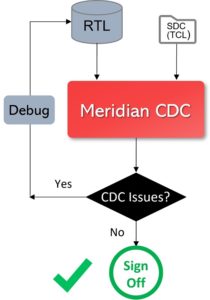

Meridian CDC is the fastest, highest capacity and most precise clock domain crossing tool in the market for CDC sign-off. It performs comprehensive structural and functional analysis to ensure that signals crossing asynchronous clock domains in ASIC or FPGA devices are received reliably.

Meridian CDC enables all aspects of CDC sign-off, including identifying issues related to metastability, loss of correlation, and glitch propagation.

The tool is specifically architected for multimode clock domain crossing analysis, Meridian CDC performs comprehensive CDC analysis with multiple clocks reaching the flops, allowing all possible clocking modes to be covered in a single run.

Its deep static analysis engines interpret multimode clock structures and automatically eliminate impossible clock and data combinations to generate high precision reports which provide true multimode CDC sign-off.

Multiple Technologies Enable Complete CDC Sign Off from RTL

Meridian CDC’s fast performance, high precision, and high capacity enables quick clock domain crossing verification, from individual blocks to billion-gate SoC designs. Additionally, it is the simplest-to-use CDC solution in the industry, with integrated debug.

The tool also generates dynamic CDC verification models which can be compiled into a user’s simulation environment to further fortify CDC sign off. Finally, CDC verification hierarchical flow delivers tremendous productivity boost with flat CDC accuracy.

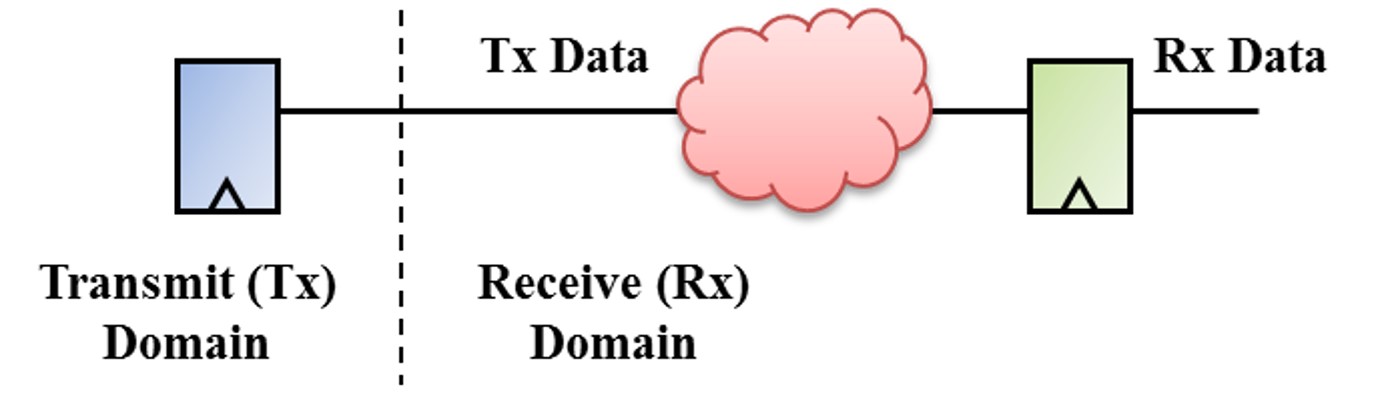

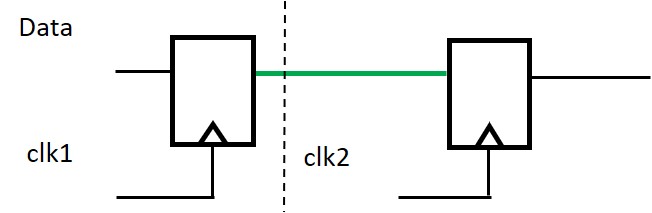

CDC Metastability

CDC bugs result from a combination of poor implementation, clock timing, and analog-like behavior in digital logic. For example, if a signal crossing from one domain to another relatively asynchronous domain arrives too close to the receiving clock edge, the captured value is nondeterministic and leads to signal metastability.

The resulting errors are nearly impossible to detect and diagnose via simulation or in the lab and cause frequent failures in the field that are expensive to fix.

Why Multimode?

Current single-mode methodology for CDC sign-off uses SDC constraints with case analysis for each mode. That necessitates the reviewing of CDC issues in each mode separately and several iterations to ensure that all modes are clean. With the rapid rise in the number of modes, it is nearly impossible to sign-off each mode individually. In addition, static timing analysis, traditionally done in single mode, has already moved toward multimode analysis. As a result, multimode SDC is more readily available to start multimode CDC sign-off.

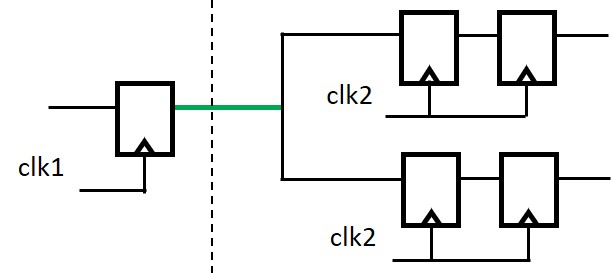

Multiple clocks feed into the flops

True Multimode CDC Sign-off

In Meridian CDC analysis is performed using multiple clocks reaching the flops. SDC constraints are applied without mode select, allowing multiple clocks to propagate to the flops.

Meridian CDC’s deep static analysis technology can automatically deduce whether certain clock interactions are not possible in certain logic areas of the design.

High Precision, Low Noise Results

Meridian CDC is the most precise solution in the market for clock domain crossing sign off.

Its proprietary static algorithms accurately interpret and deeply analyze clock domain crossing design structures. The tool then categorizes the CDC paths into safe and unsafe paths.

This results in high precision, low noise results — even for the most complex CDC designs.

Unsafe

Safe

In multimode, as the amount of CDC analysis data can increase manifold, the multimode CDC tool must be highly precise, so it leads to an efficient CDC sign-off. Meridian CDC’s proprietary technology has a holistic view of all the modes in the design which enables it to generate a high precision report.

Meridian CDC’s deep static analysis technology can automatically interpret the CDC handshake structures in a multimode context leading to low noise reports.

Meridian CDC Resources

Datasheet

Datasheet

Comprehensive CDC Sign-off

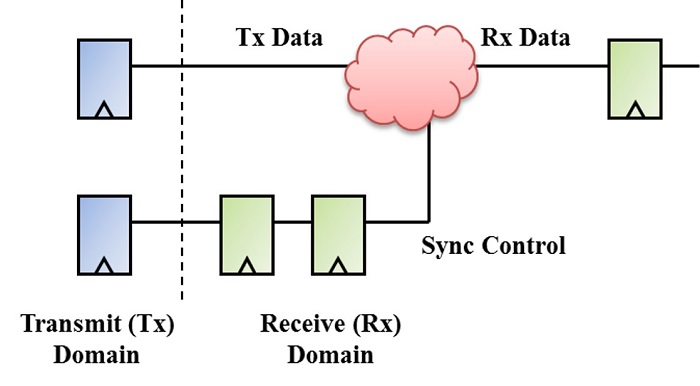

In addition to metastability, clock domain crossings can introduce other catastrophic failures in the design.

Meridian CDC comprehensively analyzes clock/reset structures and identifies all possible CDC issues including incorrect or missing synchronization, glitch potential, reconvergence, structurally unsafe crossings, and potential data/control crossings that need functional verification.

Meridian CDC supports Verilog, VHDL, and System Verilog languages and standard SDC or TCL format to read design constraints.

All CDC checks are enabled in multimode.

Loss of Data

Loss of Correlation

Smart Reporting and Powerful GUI

Meridian CDC’s smart reporting and organization enables users to efficiently focus on their designs most critical issues, regardless of the SOC complexity.

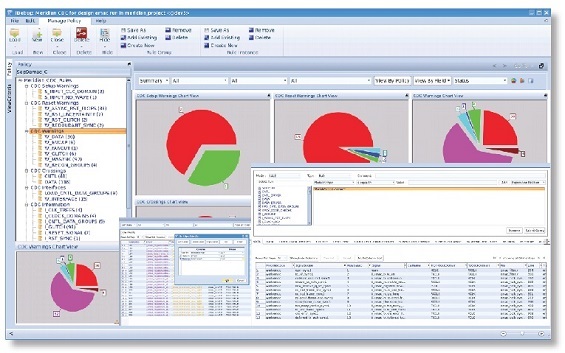

The tool provides helpful guidance, suggesting actions to help users to quickly pinpoint the problems sources. Real Intent’s design-intent debugger and analysis manager iDebug allows user configurability and programmability with its command line interface.

Meridian CDC also includes an integrated visualization tool; it has pruned schematic views that focus precisely on fault-related logic. It then directs users to related problematic RTL-source code within a few mouse clicks. This debug approach allows for easy investigation deep into complex designs to isolate the root cause for any reported warning or error.

Real Intent iDebug customized reporting for clock domain crossing warning

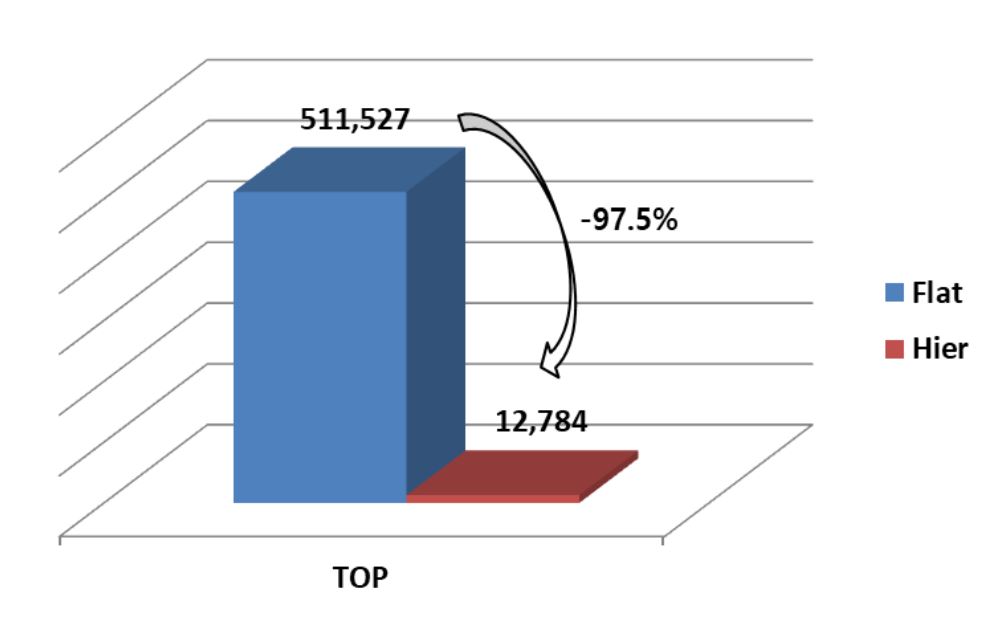

Hierarchical CDC reduces the # of violations found at the chip level

Hierarchical CDC Methodology

Meridian CDC’s hierarchical capability allows users to perform clock domain crossing verification on billion-gate SOCs within a matter of hours.

The hierarchical flow is founded on a unique transparent hierarchical model derived from block-level CDC analyses, and can be used at the chip level. This unique model provides unprecedented productivity gains with flat CDC accuracy.

As a result, it delivers seamless hierarchical debug which is equivalent in accuracy to a flat run.

Dynamic CDC Verification during Simulation

Meridian CDC’s unique Simportal capability generates dynamic CDC verification models which can be compiled into a user’s simulation environment to further fortify CDC sign-off.

Features

- Most precise multimode CDC reporting—no crossing missed

- Deep static verification technology provides unprecedented precision, ease of use, and debug

- Automatic interpretation of CDC handshake structures in multimode context

- Comprehensive: All CDC checks enabled in multimode

- Efficient debug, especially architected for multimode CDC sign-off

- Metastability-aware formal and dynamic analysis

- Flexible top-down and bottom-up hierarchical analysis accommodates different design methodologies

Benefits

- Fastest performance for quick clock domain crossing sign-off turnaround

- Highest capacity to enable CDC verification of billion-gate SoC designs

- Most precise CDC reporting using integrated analysis

- Easiest-to-use CDC solution in the industry, and is template free

- Requires single setup for multimode

- Saves debug time by avoiding analysis of crossings that cannot occur, iterations, and duplication of reviews

What Multimode CDC Users are Saying

Precision/Low Noise

“Western Digital’s enhanced clock & reset verification methodology with Meridian CDC exponentially reduced CDC sign-off noise and debug effort

“Our team caught corner-case synchronization issues because only real violations were flagged with the enhanced methodology.”

“Western Digital used to get around 800K reset related CDC violations on this SoC. Meridian CDC had zero violations and missed none of the issues.”

– Mukesh Panda, Western Digital, Case Study

Efficient Debug

![]()

“Hailo achieved successful static sign-off for edge AI processor using Meridian CDC.

“The tool’s schematic viewer made it easier to find and root cause issues; e.g., it shows clock domains in different colors.

“Hailo got good quality results from Meridian CDC within the first two weeks.”

– Guy Kaminitz, Hailo, Case Study

Multimode Saves Time

![]()

“Meridian CDC reduces our runtime massively. When we run Meridian CDC on 3 clock modes simultaneously, we save 1/2 the runtime. We only need one set-up for multimode/multi-scenario for all of our CDC cases.

“We save a ton of debug time because all our CDC violations are deduped across all clock modes and in just one place.

“Meridian also does a hierarchical flow… so, our top-level CDC runtimes/capacity are good, too.”

– Semiconductor Designer, DeepChip.com EDA Tool Report