Case Study Presentation Overview

Guy Kaminitz, vice president of VLSI, and Lotan Kantor, VLSI engineer, of Hailo discuss RTL static sign-off for their Edge AI deep learning processor in a highly pressured timeframe.

They present results that include a ramp-up time of only two weeks for Real Intent Meridian CDC, and an overall verification time reduction of five weeks from Real Intent Ascent Lint.

Hailo Background

Hailo has developed a deep learning processor for edge devices, called the Hailo-8™. It took them two years from first architecture to having the chip in-house; they now have the fully functional processor in silicon.

As of the time of the presentation, Hailo had 100 employees.

Hailo’s vice president of engineering, Guy Kaminitz, gave the first half of the presentation.

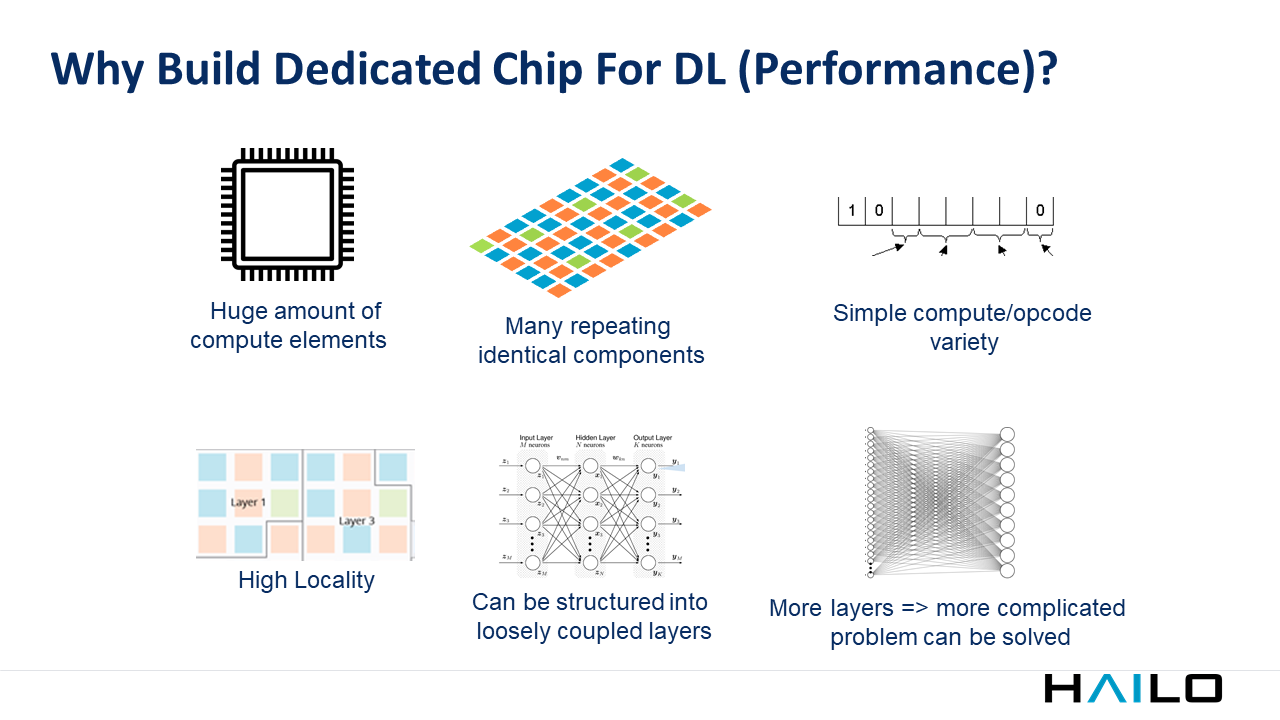

Why Build a Dedicated Chip for Deep Learning?

Guy stated that Hailo is focused on edge computing and mentioned some of their reasons for building dedicated chip for deep learning.

- There are a huge number of compute elements; a Von Neumann architecture cannot effectively handle this much parallel computing.

- There are many repeating elements in Hailo’s architecture and in neural networks in general.

- Neural networks have a locality point of view — you do not need to see the entire memory structure and compute structures. A dedicated chip can take advantage of this to provide more efficiency compared with generic CPUs.

- The layers themselves are almost independent. Thus, each layer in the neural network only needs connectivity to a small number of layers in the network. This approach gives Hailo a huge architectural benefit compared with using spread or shared memory throughout the whole SoC.

A dedicated deep learning chip provides the best performance when trying to solve complex problems, compared with solving easier tasks with a simple neural network and traditional CPU architecture.

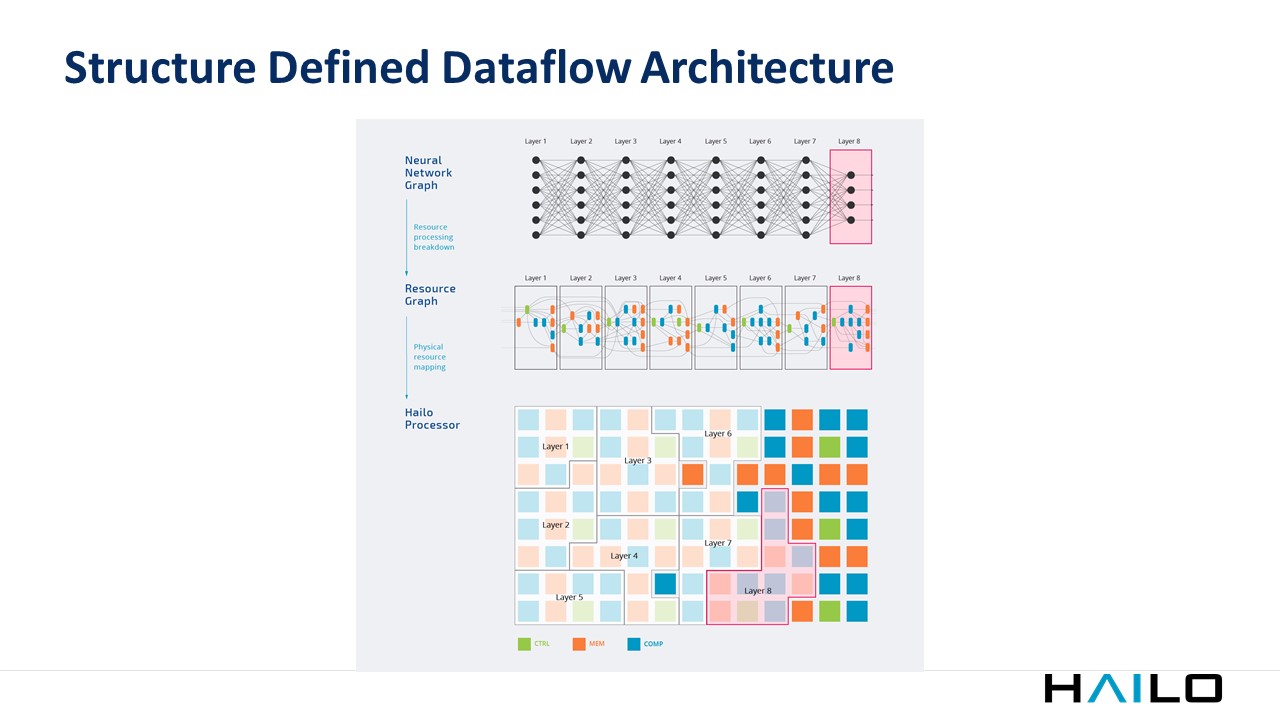

Structure-Defined Dataflow Architecture

Guy shared that Hailo’s dataflow architecture has three units: compute elements, memory elements, and control elements that can be allocated according to the customer network.

Each layer consumes the appropriate amount of chip resources.

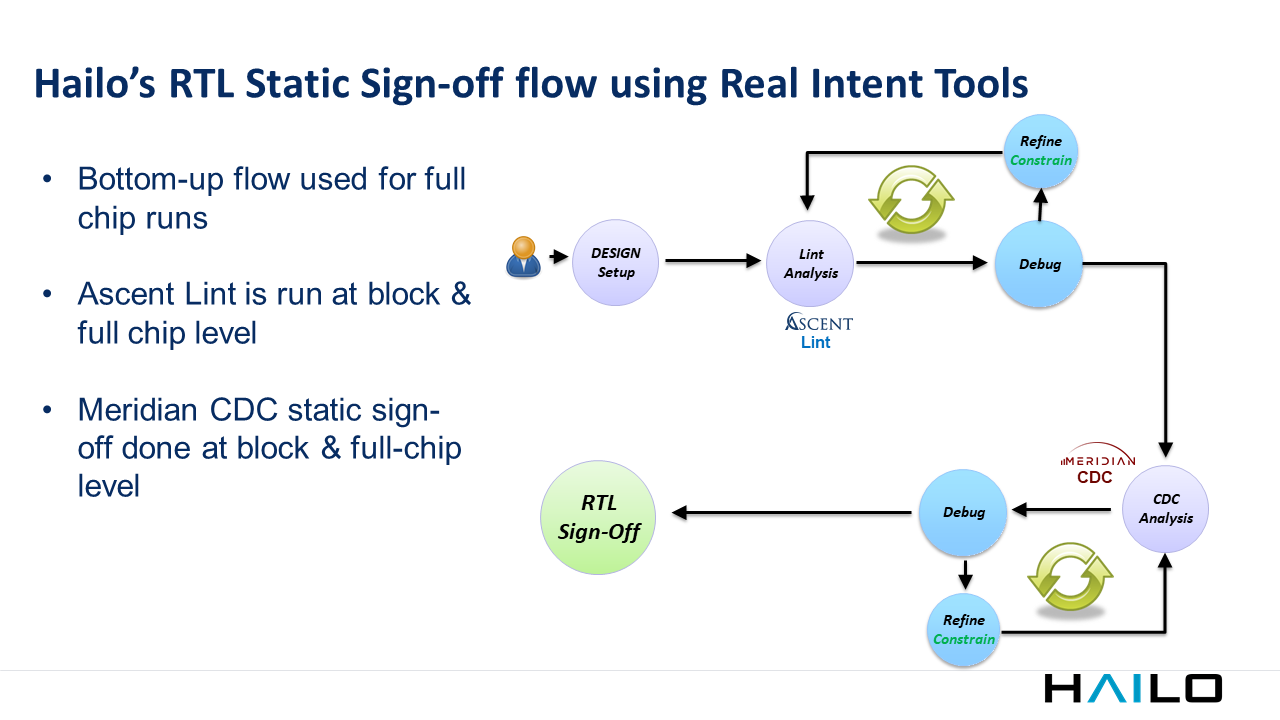

Hailo’s Static Sign-Off Flow with Real Intent Tools

Lotan Kantor, Hailo’s VLSI engineer, presented this second portion of Hailo’s talk.

Lotan shared that Hailo uses Real Intent Ascent Lint and Meridian CDC static sign-off tools.

- Their design cycle begins with RTL design; they then do RTL linting, and iterate to refine their RTL and waivers.

- They start with block-level runs and then move to full chip level.

He commented that for both Ascent Lint and Meridian CDC, the iteration cycles for running the tools, debugging, and adding constraints or waivers is very short.

This was a very important aspect for Hailo, as it helped them focus their quality time on fixing real RTL linting and clock domain crossing problems.

Fast Learning Curve for RTL Linting & CDC Sign-Off

Lotan said both Real Intent tools were very easy to ramp up and use. (When Hailo began the project, they were new to the tools.)

Ascent Lint

- Hailo was able to get initial results in almost no time. They only needed to provide the RTL file list and run the tool to get the results.

- Lotan said that Ascent Lint’s ability to help them quickly finding design bugs shortened their verification time an estimated five weeks by reducing their simulation debug time.

Meridian CDC

- The tool had a very short ramp-up, with simple easy-to-use scripts, and an intuitive way to add constraints and waivers. The tool’s schematic viewer also made it easier to find and root cause issues; for example, it shows the clock domains in different colors.

- As with RTL linting, Lotan said that the result was that Hailo was able to spend more time on quality debugging.

Clock Domain Crossing Challenges for Hailo’s Edge AI Processor

Lotan discussed Hailo’s key challenges related to CDC sign-off for their processor design, starting with a short sign-off timeframe.

Further, their design’s clock structure was complex, and their knowledge of the clock tree was scattered among several people both inside and outside their company.

Clock Domain Crossing Sign-off Results

Lotan said Hailo was able to ramp up quickly with Meridian CDC, getting good quality results within the first two weeks. He noted that while the integration of constraints from IP vendors constraints is usually tricky, the integration was relatively easy with Meridian CDC.

The company also had IP blocks from outside vendors, such as PHY and CW, which had to be addressed properly to avoid noise in CDC runs. Lotan said that Meridian CDC handled this very well.

Meridian CDC identified several CDC issues, which Hailo then fixed. Lotan said that the ability to filter the violations quickly was key to identifying real design problems.

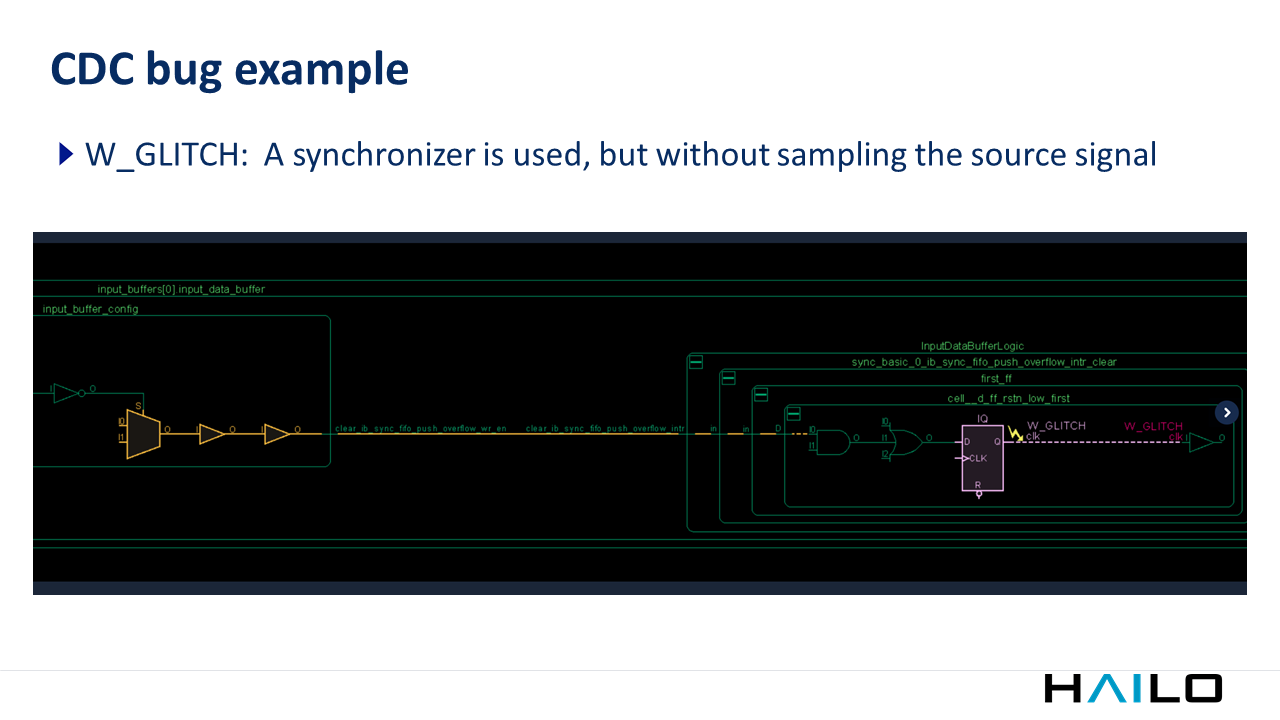

Clock Domain Crossing Bug Example

Lotan gave an example of a glitch that they found. On the left side of the graphic is an overflow signal, which originated from the yellow domain. The pink domain is the destination domain – the destination flop is a synchronizer.

The problem identified was that there was no sampling of the source signal in a source clock:

- This could cause a glitch in the synchronizer.

- The glitch could be sampled and passed on to the logic after the synchronizer which can cause unexpected results, including chip failure.

- This issue could not be discovered by a simulation tool.

Hailo found this issue and fixed it in minimal time. Their solution was very simple: Hailo did additional sampling in the yellow domain and then gave the results directly to the synchronizer.

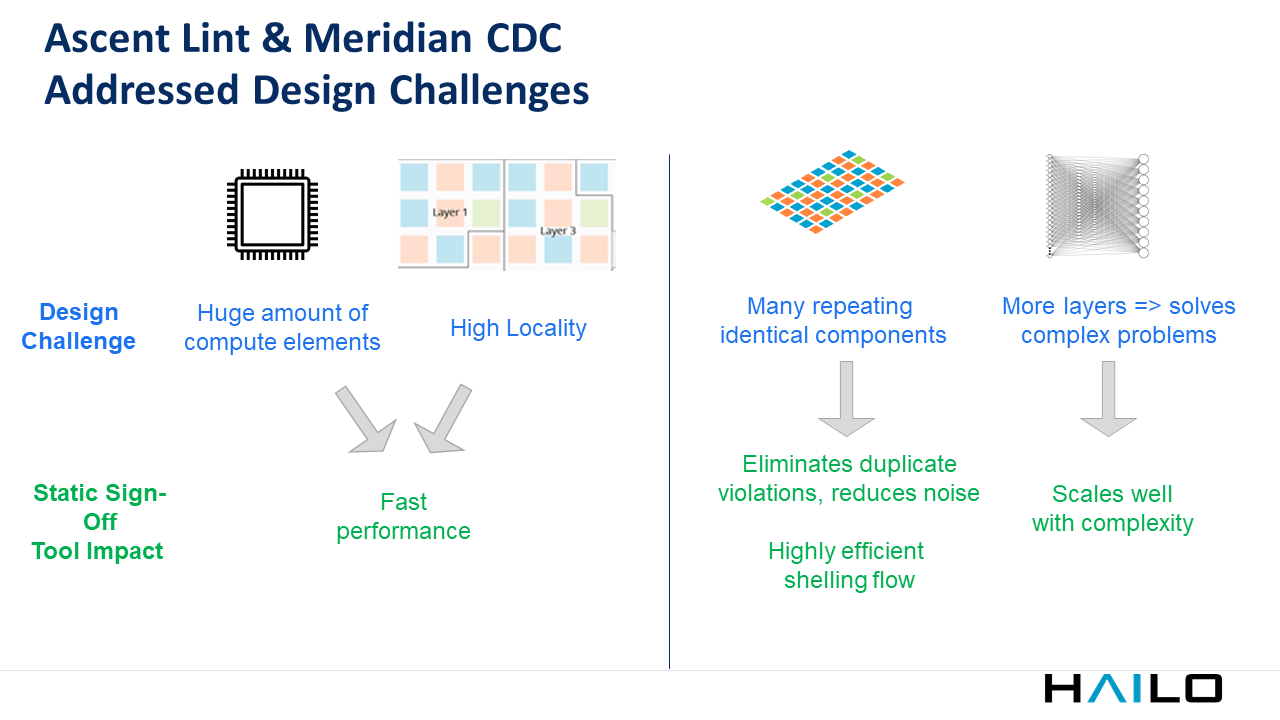

Conclusion: Real Intent Static Sign-Off Tools Addressed Hailo’s Design Challenges

Lotan reviewed how Ascent Lint and Meridian CDC addressed their specific design challenges.

- Hailo’s Edge AI processor had a huge number of compute elements. Both Real Intent static sign-off tools helped them overcome this challenge.

- The design also had many repeating and identical components, so it was very important to limit duplication violations to reduce noise in the analysis. Both tools handled that aspect very well.

- Hailo adopted a highly efficient shell hierarchical flow. Solving complex problems requires more layers; the Real Intent tools were able to scale up well with a high number of layers.

Lotan summarized, saying that both tool ramp-ups were fast – only a couple of weeks. Additionally, Hailo found multiple design issues, and shorten their design and verification time.