Reset Domain Crossing Sign-off

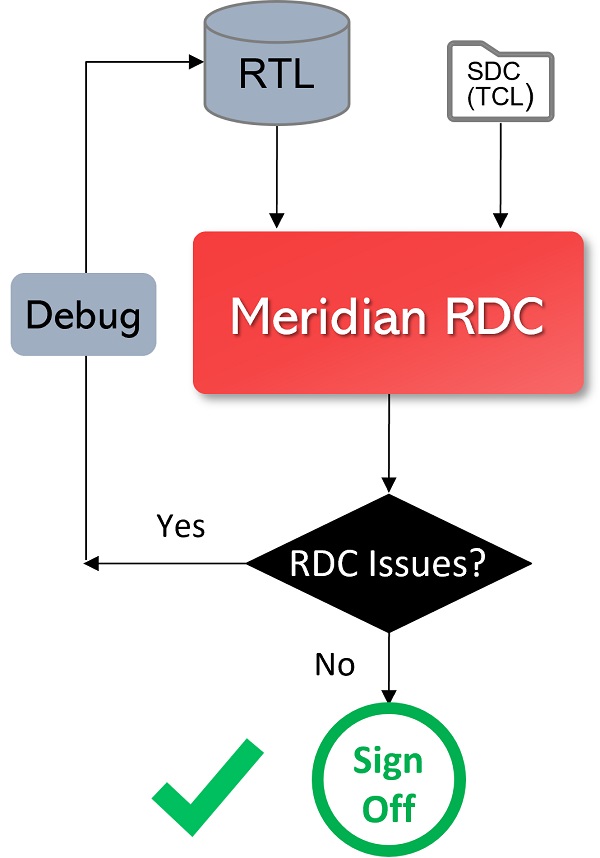

Meridian RDC is the industry’s fastest, lowest noise, multi-scenario reset domain crossing sign-off tool. It performs both structural and functional analysis to ensure that signals crossing reset domains behave reliably.

Meridian RDC identifies reset functionality problems due to

- Metastability, e.g. arising from software and/or low power resets

- Glitches on asynchronous resets

- Reconvergence of synchronized resets

Meridian RDC is the only solution in the industry that enables comprehensive, multi-scenario reset domain crossing sign-off. It requires only one setup, analyzes multiple reset scenarios in one run — in parallel for maximum speed, and produces one consolidated, low-noise violation report.

This minimizes engineering effort and debug time — dramatically improving usability in the design flow.

What is Reset Domain Crossing?

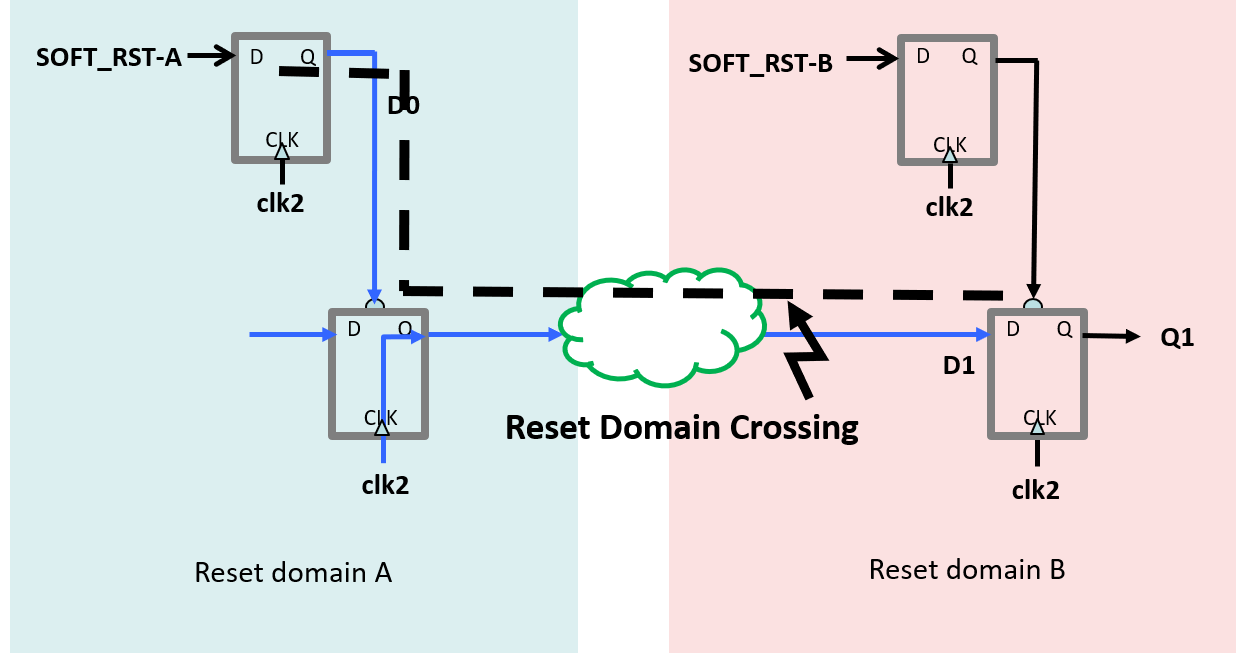

Reset domain crossing (RDC) refers to a path in the design where the source & destination elements (flops, latches, clock gates) operate on different independent resets. Reset domain crossing sign-off tools & methodologies ensure the signals crossing the reset domains function reliably.

What is Metastability?

Metastability occurs when an asynchronous reset from one reset domain causes a transition too close to the clock edge of a flip-flop in another reset domain or without a reset, causing a non-deterministic flip-flop value that propagates throughout the design resulting in functional failures.

Untimed path through the reset port

Reset Domain Crossing Chip-killer Bugs

Poor reset architecture and/or design can result in unreliable functional resets, causing intermittent catastrophic chip failures.

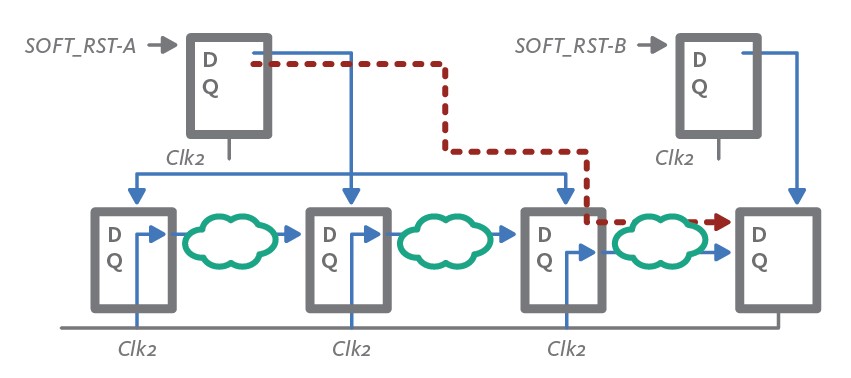

Metastability may result at a reset domain crossing when an asynchronous reset is asserted/deasserted. Glitches may cause spurious resets when an asynchronous reset is generated by combinatorial logic. Functional loss of correlation of synchronized resets may result from reconvergence.

As shown in the figure, static timing analysis (STA) constrains normal timing paths (shown in blue). But, if SOFT_RST-A asserts, while SOFT_RST-B does not assert, an untimed path is created through the reset port (shown in red). This may result in intermittent unpredictable silicon behavior.

These chip-killer errors are not caught in static solutions like STA, clock domain crossing (CDC) tools, or through simulation. They result in chip failures in the field that are difficult to diagnose and expensive to fix.

Precision Reset Domain Crossing Sign-off

Meridian RDC automatically extracts resets and reset domains and performs precise RDC analysis. Meridian RDC’s unique technology allows designers to use effective strategies to guarantee complete reset domain crossing correctness. It verifies:

- Asynchronous resets that are crossing reset domains will not cause metastability when resets are activated or de-activated

- Reconverging synchronized resets are functionally correlated

- Asynchronous resets are glitch-free

This provides best-in-class quality of results for reset integrity in the market.

Reset Groups & Scenarios

Meridian RDC allows you to define several related reset signals. You can specify the reset relationships using simple reset groups or through advanced reset scenarios.

For more precise modeling of the reset relationships, you can also include constraints that impact reset behavior. Additionally, our unique reset scenario specification capability allows you to model the reset behavior for multiple transitions and edge accurate granularity.

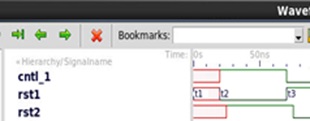

The dependencies between multiple resets can be defined in both time-based and event-based manners. By automatically generating signal waveforms from reset specifications, Meridian RDC visualizes correct reset relationships.

Lowest Noise Reports Improve Sign-Off Efficiency

Meridian RDC provides the lowest noise reports in the industry due to its unique functional analysis and observability analysis.

Functional Analysis. RDC functional analysis enables accurate identification of all the safe paths, reporting only actual errors for the user to review. This inherently reduces noise in reporting and avoids the tedious review, debug and waive process.

Observability Analysis. Reporting noise is reduced further by analyzing whether the primary metastability violation between a reset flop and metastable flop can propagate from the metastable flop into other reset domains.

Hierarchical RDC Flow with Flat RDC Accuracy

Meridian RDC’s advanced hierarchical flow helps design teams effectively manage reset domain crossing sign off even for extremely large designs, providing unprecedented productivity gains. The high level partitioning significantly improves runtime by dramatically reducing the volume of data to be analyzed; RDC analysis can be performed on billion gate SoCs in a matter of hours.

Additionally, late RTL changes that can affect entire chip are contained to enable successful RDC Sign off.

Meridian RDC utilizes a unique transparent hierarchical model at the chip level, derived from block level RDC analysis. Each IP or block can be independently verified and then assembled at a higher level. Meridian RDC’s hierarchical database model saves fully accurate design information, in contrast to black boxes with only abstracted information at the ports.

The result is seamless debug that is equivalent in accuracy to a flat run – for fully confident reset domain crossing sign off.

Smart Reporting and Powerful GUI

Meridian RDC’s smart reporting keeps users focused on important issues through efficient organization of findings. Helpful guidance and suggested actions help users pinpoint the source of the problems quickly. Real Intent’s state-of-the-art design intent debugger and analysis manager—iDebug—provides for user configurability and programmability with its command line interface (CLI). All the reset domain crossing analysis data is stored in a database that can be accessed through the CLI. Users can customize the debug methodology to match their design flows using spreadsheet reports, graphical reports, scripting, and so on.

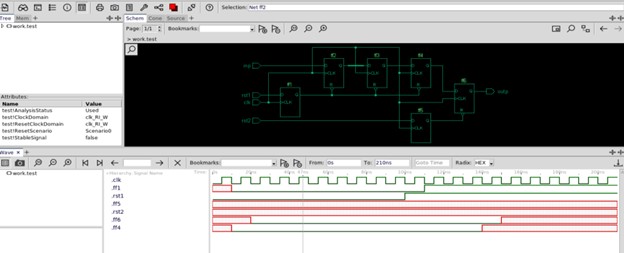

Meridian RDC supports an integrated visualization tool. Pruned schematic views focus on fault-related logic, and with a few mouse clicks, users are directed to the RTL source code that caused the problem. This debug approach allows for easy investigation deep into the design to isolate the root cause for any warnings and errors.

Advanced Debug Capability for Faster Root Cause Analysis

Meridian RDC provides advanced functionality for engineers to efficiently debug the reported violations.

Complete waveform visualization in iDebug enables comprehensive exploration of debug data. All design signal waveforms can be displayed for each metastability violation for efficient and seamless root cause analysis.

Additionally, engineers can quickly zoom in on targeted flip flops and/or reset scenarios, utilizing iterative debug flows for faster turn-around.

RDC Simportal helps ensure that the reset scenario specifications in RDC analysis are consistent with the simulation behavior. Engineers can generate SystemVerilog assertions to model the reset scenario specifications and then use the assertions in design simulations to confirm the expected behavior.

RDC Analysis Parallelization Accelerates Performance

Meridian RDC utilizes parallelism to accelerate performance for both flat and hierarchical reset domain crossing runs. This unique parallelization of RDC verification flow provides order of magnitude improvement in run time and debugging effectiveness.

The parallel runs can be on multiple cores on the same server or distributed across a server farm.

What Meridian RDC Users are Saying

High Precision, Low Noise

Unlike [a competitor’s tool], Meridian RDC’s engine is specifically customized for RDC. This means that Meridian RDC can take advantage of more precise scenarios and constraints from our designers.

The result is that the Meridian RDC violation reports have 2x-9x less noise as [a competitive RDC tool].

– Semiconductor Designer, DeepChip.com User Benchmark

Multi-Scenario / Multimode

![]()

Meridian RDC automatically runs all our scenarios in parallel. Without this ‘multi-scenario’ feature, we’d have to run RDC analysis sequentially for each scenario, which would take more manual effort and more time.

It generates one consolidated report as to which conditions are and are not being met, which minimizes our review time.

– Semiconductor Designer, DeepChip.com EDA Tool Report

Efficient Debug

![]()

Meridian RDC uses the same iDebug debugging tool that Meridian CDC uses; the nice thing is we can see the schematic for the RDC violation, plus we have the option to annotate VCD files for signal values.

Meridian RDC generates assertions in SVA format to help debug any issues later using a formal tool or simulator.

– Semiconductor Designer, DeepChip.com EDA tool report